## Cheryl Watson's

2004, No. 2

# TUNING Letter

A PRACTICAL JOURNAL OF z/OS TUNING AND MEASUREMENT ADVICE

#### Inside this issue...

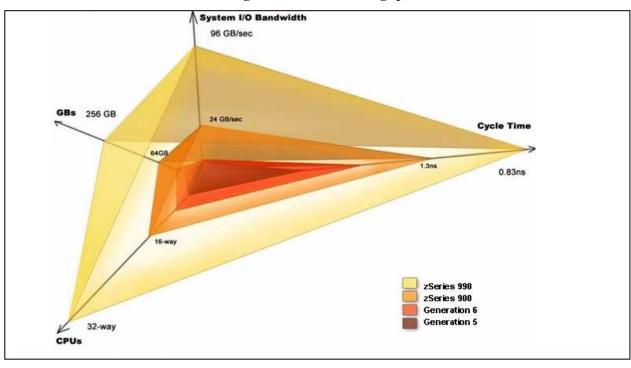

This is a special issue; one that we've been researching for more than six months. The z990 series machines that debuted in September 2003 are the most powerful machines that IBM has ever produced. But not everybody is happy with them. It's taken us several months of investigation, but we think we understand the reasons behind the apparent underperformance. That's the focus of this issue; our analysis starts on page 26.

New customized LSPR workload mixes are at the heart of this problem. So before we can discuss z990 performance in depth, we need to provide an introduction and update to LSPRs (page 3). It will probably surprise most of our readers to discover their workloads probably don't match the traditional workload LSPR definitions.

Another factor is the move to faster and fewer processors. Although we wrote about this situation in 1998, it's more pronounced when moving to the faster z990s. So we've updated that article and have included it on page 40.

The 40<sup>th</sup> anniversary of the IBM S/360 was on April 7, 2004, and it brought a large number of significant announcements. We describe these announcements on page 45 in our *What's New?* section.

All of the performance results in this issue were obtained using our **BoxScore** software product. BoxScore was designed to show the differences in actual versus expected speed and capacity when moving to a new machine or environment. You'll need BoxScore or something like it to make sure that you got what you paid for.

The next issue is almost complete and will follow this one shortly.

We think this is one of the most valuable issues that we've ever produced. We hope you think so too.

#### This Issue:

| Management Summary2          |

|------------------------------|

| Focus: LSPR Update           |

| History3                     |

| IBM's Sizing Tools10         |

| New Workloads12              |

| z900 LSPRs16                 |

| z990 LSPRs20                 |

| z890 LSPRs23                 |

| Bibliography24               |

| Focus: z990 Expectations     |

| BoxScore Results26           |

| Reasons29                    |

| z900 to z990 Migration30     |

| More BoxScore Results33      |

| Observations37               |

| Our Recommendations38        |

| Processor Upgrades           |

| Typical Problems40           |

| Moving to Faster CPs 42      |

| Moving to Fewer CPs43        |

| What's New?                  |

| z89045                       |

| zAAP48                       |

|                              |

| "Baby" Shark50               |

| z990 Enhancements51          |

| z/OS 1.6 Additions51         |

| Other Announcements 52       |

| Control Block Updates 53     |

| ECMB Update54                |

| Change in Throughput55       |

| Cheryl's List #87, 8856      |

| Supplements:                 |

| zSeries CPU Chart - Apr 2004 |

| OS/390 CPU Chart - Apr 2004  |

## Cheryl Watson's **TUNING** Letter

## Management Summary

This entire TUNING Letter is devoted to the research we've been doing over the last six months regarding z990 expectations versus actual performance. The z990s became generally available in September 2003, and we started hearing rumors of underperformance in November. Then we started getting results back from customers using our BoxScore software product, which is designed to measure performance differences associated with hardware or software changes. The results didn't look good - with many customers reporting a 10 to 15% underperformance for batch and a 15-20% underperformance for CICS using the traditional methods of comparison.

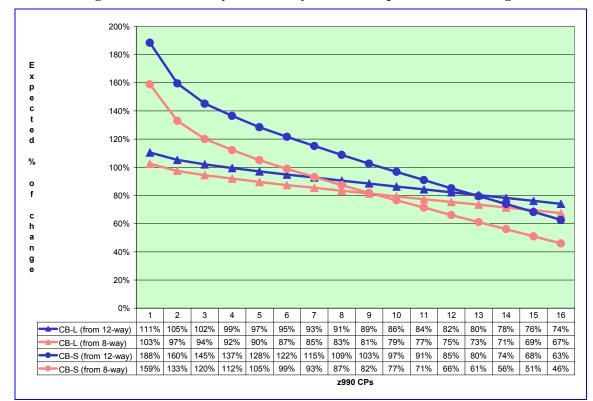

At the end of 2003, IBM began to realize that most of the published LSPR ratings apply only to about 20% of the z990 customers. They have found that about 80% of their customers now run a low I/O density workload mix, which most closely matches the CB-L (commercial batch long) workload. To the casual observer, this would seem like good news because the CB-L workload tends to result in a higher MIPS rating than most other workloads. But, in fact, it's bad news: The increase in MIPS, when moving from a z900 to a z990 with the same or fewer processors, is less for CB-L than for any other workload. In one example, if you were expecting a 1000 MIPS increase in capacity based on

an average MIPS rating, the use of CB-L ratings would lower that expectation to be only a 900 MIPS increase.

We have confirmed that when using these CB-L ratings most batch work falls within IBM's guidelines for acceptable performance (plus or minus 5% from the expected ratings). We have some concerns about this range of plus or minus 5% when sizing your capacity. On these very large machines, that 5% could amount to a range of 500 MIPS or more.

From our customers' BoxScore runs, we have also concluded that CICS is still not meeting even the minimal CB-L workload expectations. They are finding that CICS work is still taking from 5-10% more CPU than expected. We don't know why this occurs; IBM disagrees with us, but we stand behind our results. (They don't use CICS transaction level analysis, and we do.)

There are two main points in this issue: 1) You must approach the sizing of new machines in a different manner if you expect IBM to warranty your expectations; and 2) It's extremely important to insure that you received the added capacity that you purchased.

## Cheryl Watson's **TUNING** Letter

2004 Number 2 (Vol. 14, No. 2) Published 6 times a year by Watson & Walker, Inc. www.watsonwalker.com

**Publisher:** Tom Walker

Executive Editor: Cheryl Watson

Editor: Clark Kidd

Production Manager: Linda May

2004 SUBSCRIPTION RATES: Electronic version (CD-ROM & email) \$765 per year. Printed version \$545 per year, \$600 outside North America. Payment may be made by a check drawn on a U.S. bank, a money order, any major credit card, or by wire transfer. Issues are mailed via first class mail. All back issues are available. Send all correspondence to: Watson & Walker, Inc., 2130 Bispham Road, Sarasota, Florida 34231, USA. Tel: 800-553-4562 or 941-924-6565. Fax: 941-924-4892. For customer service, send email to admin@watsonwalker.com.

© 2004 Watson & Walker, Inc. All rights reserved. ISSN #1079-6606. Reproduction of this document is permitted only for internal use at the physical address where it was received. Permission is required for exceptions to this rule.

All IBM and other product names are trademarks of their respective owners.

Note: Implementation of any suggestions contained in this newsletter should be preceded by a controlled test and is the responsibility of the reader.

## Focus: LSPR Update

e're concerned that many installations seem to be seeing disappointing results when they move to the new z990 processors. We think there are several reasons for this disappointment, which we'll explain in more detail starting on page 26. But for a complete understanding of what has happened, we first need to provide an update and explanation of IBM's Large System Performance Reference (LSPR) methodology that they use for processor sizing. Please review this section before continuing to the next article on z990 Expectations. It's critical to understanding what has happened over the last couple of years.

IBM publishes their LSPR tables and methodology on one of their Web sites [see REF001 in our Bibliography on page 24]. We've explained this LSPR methodology in our CPU Chart [REF002] and in previous TUNING Letters [REF003]. But there are several things that we've recently discovered that are very important to understanding the performance of the z990s. This article covers the following topics:

- History

- IBM's Sizing Tools

- New Benchmarking Workloads

- z900 LSPRs

- z990 LSPRs

- z890 LSPRs

- Bibliography

## History

#### **MVS LSPRs**

Many years ago, IBM designed a set of seven benchmark workloads to represent the types of work being run by their customers. These workloads were TSO, CICS, DB2, IMS, CB84 (commercial batch using traditional techniques), CBW2 (commercial batch using newer data-in-memory techniques and heavy DB2), and FPC1 (scientific and engineering, and also representative of SAS work). We describe these workloads in detail in our OS/390 CPU Chart. These workloads were used over the course of several MVS releases.

IBM then ran stand-alone benchmarks for each workload on different machines to determine the ITR (Internal Throughput Rate) ratio between each machine and a "base" machine, which was given an ITR of 1. The ITR is calculated as the units of work completed divided by processor busy time in seconds. When an ITR is compared to a base machine's ITR, the result is an ITRR (ITR ratio). The higher the resulting ITRR value, the greater the capacity for that workload. A machine with an ITRR of .5 has only one quarter the capacity of a machine with an ITRR of 2.0. For our CPU Charts, we convert the ITRRs to MIPS so that they are easier to understand.

#### MIX - MIX Workload

At the same time, IBM also provided a mixed workload (which we have always named "MIX"). IBM calculated this MIX workload as the harmonic mean of the benchmarks for five of the seven workloads: TSO, CICS, DB2, IMS and CB84.

The harmonic mean is used instead of the arithmetic mean because these values represent rates instead of totals. The MIX workload ITR is calculated as:

The value of .20 is used because it represents the percentage of each of the five types of workloads. As an example of the difference between the harmonic mean and the arithmetic mean for the z990 2084-332, the arithmetic mean would produce a total MIPS estimate of 9249 MIPS, whereas the harmonic mean would produce our published total MIPS estimate of 9059. This difference is minor and almost unnoticeable for small processors, but becomes more significant as the speed of the processor increases.

An excellent CMG 2000 paper was written about the use of harmonic mean by **Dr. Sudhir R. Nath** of Wells Fargo Service Company [REF009].

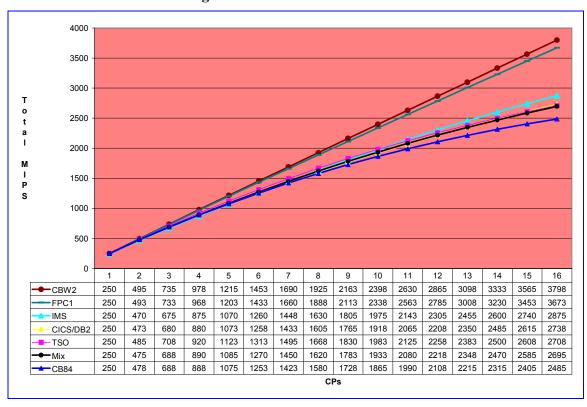

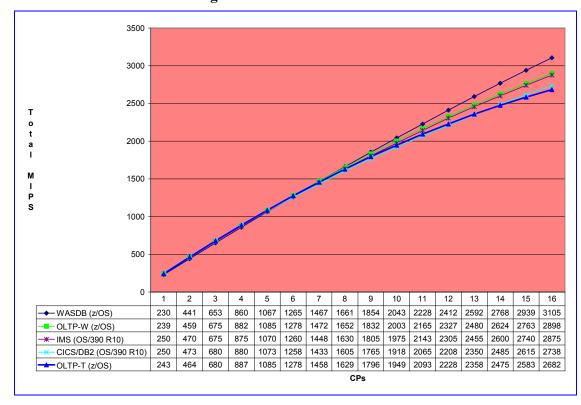

Figure 1 - OS/390 LSPRs for z900s

#### Change in CICS & DB2 LSPRs

In June of 1999, the IBM LSPR group changed the benchmark jobs to more adequately reflect the workloads commonly being run in the field. In doing so, they combined the CICS and DB2 workloads into one benchmark and changed the base operating system from OS/390 R1 to OS/390 R4. IBM used the 9672-R15 processor as a base machine. The new MIX workload was the harmonic mean of the TSO, CICS/DB2, IMS and CB84 workloads. This greatly changed the meaning of MIX, because it caused TSO, IMS and CB84 to each become 25% of the workload instead of 20%, and CICS/DB2 was reduced from 40% to 25% of the workload.

Figure 1 shows an example of these workloads for the z900 models 1C1-1C9 and 110-116 using the OS/390 LSPRs after this change in 1999. We have converted the ITRRs to MIPS, but you can see the wide variation at the higher n-ways between CBW2 and CB84. Notice that the MIX is quite low in this chart because the FPC1 and CBW2 workloads are not used in the MIX.

#### Introduction of 64-bit LSPRs

In December of 2001, IBM produced a new set of LSPR ratings based on OS/390 R10 running on a z900 2064-1C1 base machine. What was very confusing about this set of ratings was that the TSO and CICS/DB2 workloads were run in 64-bit mode, but the other workloads were run in 31-bit mode. The MIX workload of TSO, CICS/DB2, IMS and CB84 was, therefore, a mix of incompatible (and physically impossible) benchmarks.

#### zSeries LSPRs

In May of 2003, IBM once again changed the workloads. These benchmarks were run using z/OS 1.4 and based on a z990 2084-301 machine. IMS, CB84 and CBW2 remained the same benchmarks, but were renamed to OLTP-T (OnLine Transaction Processing - Traditional), CB-S (Commercial Batch - Short) and CB-L (Commercial Batch - Long), respectively. The TSO and FPC1 workloads were dropped. The CICS/DB2 workload was modified to include a front-end Web access and was renamed to OLTP-W (OLTP Web-Enabled). And a new workload, WASDB (WebSphere Application and Database), was introduced. All of the workloads were run in 64-bit mode. The new MIX workload was now calculated as the harmonic mean of these five: OLTP-T, OLTP-W, CB-S, CB-L and WASDB. These are the current workloads for the zSeries and are described below.

From our perspective, there were two major flaws in these changes. According to IBM, they dropped TSO because it no longer represented a significant workload in most installations. This has not been our experience, and we would have liked to see the TSO benchmark retained. Secondly, there have been no published comparisons for these new workloads running in 31-bit mode and in 64-bit mode. This makes it impossible to determine what effect the architecture had on the results. This would have been extremely useful information and we wish it had been published and made available. Based on past experience, we believe that TSO will tend to match the MIX workload.

Another difference in the May 2003 LSPRs was the addition of PR/SM. Prior benchmarks had been run in basic mode; all the new benchmarks were run in LPAR mode. Thus, the overhead of running in LPAR mode (typically .5 to 1.0 percent) is now included in the LSPR ratings. Remember that the majority of "LPAR overhead" in most installations comes from multiple LPARs that are trying to share the same physical CPs. This overhead increases as the number of logical CPs exceeds the number of physical CPs. Because the LSPR benchmarks never use more logical CPs than available physical CPs, this larger (and more variable) overhead that many users will experience is not re-

flected in the LSPR ratings. We've written about LPAR overhead several times in our TUNING Letters. Please see REF015 and REF016 for some articles on this topic.

Here is a more detailed view of each of the new workloads (these descriptions come from our zSeries CPU Chart):

#### **CB-L MIPS - Commercial Batch Long Job Steps**

The CB-L workload is the same as the previous CBW2 workload, but has been renamed. This is a commercial batch workload that is most representative of new applications that exploit ESA functions, such as data in memory. It consists of programs written in C, COBOL, FORTRAN and PL/I. The steps include sorts, DFSMS utilities, compiles, VSAM and DB2 utilities, SQL processing, SLR processing, GDDM graphics and FORTRAN engineering routines. There is a lot of JES processing, and the workload spends about 50% of the time performing DB2 activities.

Even though this newer CB-L and the older CBW2 represent the same types of work, they are difficult to compare. If you are trying to compare CB-L MIPS with the CBW2 MIPS from an older CPU Chart, be aware that the CBW2 workloads were run in 31-bit mode on OS/390 R10, but the CB-L workloads are now run in 64-bit mode on z/OS. Therefore, you can't make a reliable comparison between the two workloads.

#### **CB-S MIPS - Commercial Batch Short Job Steps**

The CB-S workload is the same as the previous CB84 workload, but has been renamed. This represents a typical, traditional, view of commercial batch work. This workload consists of COBOL, Assembler H, and PL/I programs, along with compilers and utilities such as DFSORT. The BSAM, QSAM, BDAM, and VSAM access methods are used.

Once again, it is problematic to try and compare this CB-S with the older CB84 workload. The CB84 MIPS from our older CPU Chart represent work run in 31-bit mode on OS/390 R10. But the CB-S MIPS represent workloads run in 64-bit mode on z/OS. Therefore, you can't make a reliable comparison between the two workloads.

#### WASDB MIPS - WebSphere Application Server and Data Base

This is an entirely new workload that was created for the z/OS LSPRs. This workload uses WebSphere applications and a DB2 database. It contains Java classes, Java servlets, Java Server Pages (JSPs) and Enterprise Java Beans (EJBs). It emulates an online brokerage application and was written using IBM VisualAge for Java and WebSphere Studio tools.

#### OLTP-W MIPS - Web-enabled On-line Workload

The OLTP-W workload is similar to the previous CICS/DB2 workload, but has been changed to have a front-end Web-enabled access. This is very similar to most of the first Web-enabled applications in most installations. It has ten transaction types accessing DB2 databases. CP/SM (CICSplex/System Manager) is used to manage an MRO (Multi-Region Option) complex using a ratio of 1:3 between TORs (Terminal Owning Regions) and AORs (Application Owning Regions). These transactions are typical of an order entry and product delivery system.

The LSPR documentation provides more details on the architecture of the workload: "The J2EE (Java 2 Enterprise Edition) application for legacy CICS transactions was created using the CICS Transaction Gateway (CTG) external call interface (ECI) connector enabled in a J2EE server in WebSphere for z/OS V4.0.4. The application uses the J2EE architected Common Client Inter-

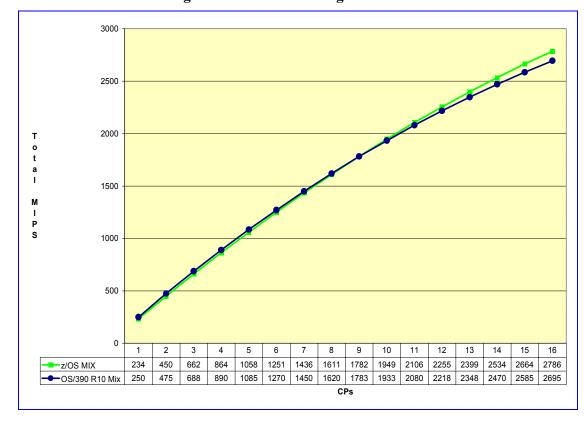

Figure 2 - z900 MIX Using Two LSPRs

face (CCI). Clients access WebSphere services using the HTTP Transport Handlers. Then the appropriate servlet is run through the webcontainer, which calls EJBs in the EJB Container. Using the CTG ECI, CICS is called to invoke DB2 to access the database and obtain the information for the client."

Because the Web-enabled front-end has been added to this workload, you can't make a reliable comparison between this OLTP-W workload and the previous CICS/DB2 workload.

#### **OLTP-T MIPS - Traditional On-Line Workload**

The z/OS LSPR OLTP-T workload is the same as the previous IMS workload. It was renamed because the IMS workload produces similar performance to the CICS DLI applications and can be used for benchmarking both types of traditional online workloads. There are twelve transaction types. Enough MPRs (Message Processing Regions) are started to bring the system to the desired utilization (70% and 90%) without causing contention within an MPR. The DLI HDAM and HIDAM access methods are used with VSAM and OSAM databases. Batch Message Processing regions (BMPs) are not included.

If you are trying to compare the IMS MIPS from an older CPU Chart with the OLTP-T MIPS, be aware that in LSPRs up through OS/390 R10, the IMS workloads were run in 31-bit mode, but the OLTP-T workloads are run in 64-bit mode. Therefore, you can't make a reliable comparison between the two workloads.

Figure 3 - z900 MIX Using Two LSPRs

#### Comparing Different LSPRs

IBM recommends that you not compare LSPR ratings that are based on different operating systems and different machines. We absolutely agree. That is why we have different CPU Charts that correspond to the different LSPR benchmarks. Our zSeries CPU Chart is based solely on the z/OS 1.4 benchmarks that are compared to the 2084-301. Our OS/390 CPU Chart is based on several of the benchmarks, but we indicate the LSPR tables used for each analysis and recommend that you not compare machines whose MIPS are not based on the same set of tables.

But we think it's important to understand how these LSPR versions differ because we know some installations will end up comparing them, despite the warnings. If you're going to do something dubious, you should at least understand the risk that you're taking. We've included several plots to help understand the difference in ratings. Here are some observations:

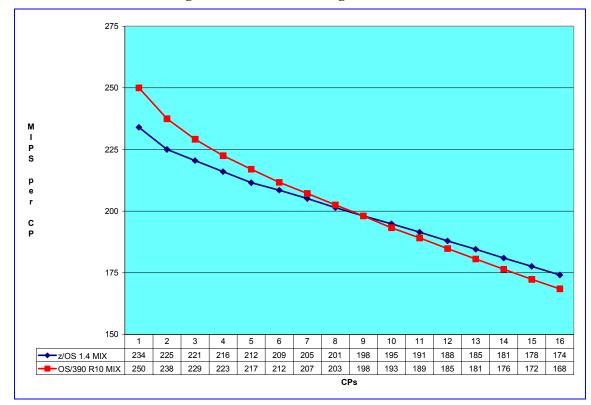

- 1. Figure 2 shows the OS/390 versus z/OS MIX MIPS for one of the z900 series machines (models 1C1-1C9 and 110-116). At the high end that plots 16 CPs, there is a difference of about 90 MIPS or about 3%. This chart refers to the total MIPS, or the capacity of the machine, based on two different sets of benchmarks.

- 2. Figure 3 shows a slightly different view of the same data. This shows MIPS per CP, which represents the speed of each CP. There are two things to notice from this plot. First, the scale of a plot can give you a very different view. Look at the 1-way. In Figure 2, the one-way capacity looked the same, simply because of the scale. In Figure 3, we see that the largest change in speed occurs in the 1-way rather than the 16-way. There is

Figure 4 - z900 Batch Workloads

actually a 7% difference in the speed of the 1-way compared to a 3% difference in the speed for the 16-way. The second thing we see is that the OS/390 R10 LSPRs result in higher MIPS for anything less than a 9-way, similar MIPS for a 9-way or 10-way, and lower MIPS for anything greater than a 10-way.

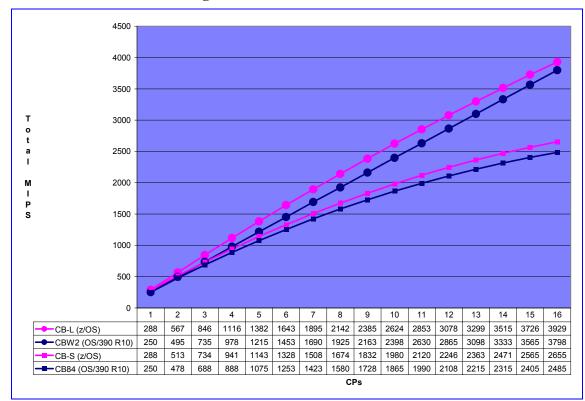

- 3. We also wanted to see how the workloads that are supposed to be fairly similar compare to one another. Figure 4 compares the associated MIPS for CB-L (z/OS 1.4) and CBW2 (OS/390 R10) workloads. See the top two lines. They are fairly close. The same is true for the older CB84 and newer CB-S (lower two lines). What's most important to note is that CB-L is used as part of the MIX workload for z/OS, but CBW2 is not used as part of the MIX workload for OS/390. This is one of the reasons that the z/OS MIX MIPS are higher than the OS/390 MIX MIPS in Figure 2.

- 4. Figure 5 shows a similar plot for the online workloads. Two interesting things show up here. First, the WASDB workload is the most effective at the higher CP levels. Secondly, the OLTP-W workload (that is a modification of the older CICS/DB2 workload) tracks more closely with the older IMS workload; and the OLTP-T workload (that is based on the older IMS) tracks more closely with the older CICS/DB2 workload. We have no explanation for this.

#### Summary

It is reasonable that IBM must make changes to their LSPR workloads to more accurately reflect the workloads being run in today's installations. Because of the changes, however, it makes it very difficult to determine whether the change in ITRR comes from the change in architecture (31-bit versus 64-bit), the host software (OS/390 to z/OS) or the base machine (z900 versus z990). In addition to

Figure 5 - z900 Online Workloads

this, the meaning of the MIX workload changes even more because of the variability mentioned above and the differing combinations of workloads. This is one of the many reasons that IBM does not recommend using the MIX workload for capacity estimates. We don't approve of that either. We also know that most installations use only the averages. As we shall see, this also has its drawbacks. Estimates by workloads provide the only meaningful results, but there are some problems even with that technique.

## IBM's Sizing Tools

IBM has several free tools to help customers plan for an upgrade. (These are in addition to the IBM fee-based consulting services.) The tools are available from your IBM representative or IBM business partner, and we don't really understand why more people don't take advantage of them. A brief description of these tools and some additional tools and services can be found in Appendix C of IBM's LSPR manual [REF004].

There is little published information about the tools other than a brief description in the LPSR manual, but you can obtain additional information from your representative. **JoAnne Brown** of IBM introduced some of the tools at session 2513 at the last SHARE [REF005] and showed the use of the zPCR tool along with some sample output. The tools are:

**zPCR** - Processor Capacity Reference for zSeries. This is a PC-based tool that provides capacity relationships for zSeries machines. You can download data into a spreadsheet from the RMF Overview Report and the RMF CPU Activity Report.

- **PCRW** Processor Capacity Reference (z800, z900 and earlier). This is similar to zPCR, but uses the OS/390 LSPRs instead of the z/OS LSPRs. A similar tool, PCR, can be used for older S/390 machines. Older machines running in LPAR mode can also use the LPAR/CE tool.

- LPAR/CE LPAR Capacity Estimator. This is another PC-based tool that helps an installation understand the impact of changing the LPAR configuration of a machine. It also provides guidance when moving to a different machine in LPAR mode.

- CP2000 Performance Analysis and Capacity Planning. This is a PC-based tool, but has a mainframe component to collect the data it needs from SMF and RMF. This tool performs functions including capacity estimates, health check analysis, CPU analysis, workload analysis and many others. Graphs are provided.

- SPSSZR S/390 Parallel Sysplex Quicksizer. This PC-based tool provides capacity planning recommendations for parallel sysplex environments.

- SOFTCAP Software Migration Capacity Planning Aid. This tool is the only one available for download by the customer. It is PC-based and helps you understand the impact of moving between architectures, machines, operating systems or WLM goal/compat mode. [REF002]

- **BWATOOL** Batch Workload Analysis Tool. This is an MVS batch job that processes SMF type 30 and type 70 records in order to analyze batch jobs. CPU time and elapsed time are analyzed for recommendations on the best processor matches or the critical path.

- Unknown Capacity analysis software. Although we don't know the name of this software, the WSC team has products to analyze how well your new machine has met its capacity estimates. It's quite similar to our BoxScore, differing (from what we can tell) in its use of weighted means rather than average percent of change. This tool uses special customized workloads (described below) in order to estimate and confirm the new processor's capacity. We explain more about the weighted means on page 34.

When we polled the attendees at Cheryl's last SHARE "Hot Flashes" session, only four to five people out of more than 250 indicated they had ever used these tools. That's a shame! Before your next upgrade, be sure to contact your IBM representative for access to these tools.

Of course, if you want to work a bit harder, you can do much of this work on your own after reading the LSPR manual and understanding the concepts of ITRRs, harmonic means, and the techniques for capacity planning.

## New Benchmarking Workloads

#### New Customized Workload Mixes

One of the most useful things that came out of JoAnne's SHARE session was a description of some new customized workload mixes that IBM is now using to characterize customer work: 'custom online', 'custom other' and 'low I/O density'. The workloads that we previously described (CB-L, CB-S, etc.) are now called 'primitives', and the new customized workload mixes are created using a combination of the primitives. **Walt Caprice** also mentioned these three workload mixes in his SHARE session [REF006].

When doing capacity planning or sizing with these tools, IBM typically divides the customer's workloads into two categories: online work (those workloads requiring a user response, such as CICS and IMS) and non-online work. They then use customized workload mixes for these two types of work. As an example, the custom online workload mix is the average of the WASDB, OLTP-W and OLTP-T primitive workloads. Of course, you can modify these combinations of primitives if you feel that your workloads are weighted more heavily towards specific types of work.

The first two new workload mixes have recently been added to our CPU Chart and BoxScore product:

#### **CUSONL - Custom Online Workload Mix**

The Custom Online workload is a custom workload mix designed for online applications. It is computed by taking the harmonic mean of the WASDB, OLTP-W and OLTP-T primitive workloads.

This is a specialized zSeries workload mix that you will not find in IBM's LSPR tables, but it may prove to more accurately meet your needs if you run the type of workload described.

#### **CUSOTH - Custom Other Workload Mix**

The Custom Other workload mix is designed for non-online applications. It is computed by taking the harmonic mean of the CB-L workload value and the CB-S workload value.

Again, this is a specialized zSeries workload mix that you will not find in IBM's LSPR tables, but it may prove to more accurately meet your needs if you run the type of workload described.

#### Low I/O Density Workload Mix

Additionally, it is IBM's belief that a large percentage (80% or so) of their customers now run in a "low I/O density" environment on z990s. IBM defines this as less than 30 DASD I/Os per second per unit of CPU usage as measured in MSUs. According to IBM, this situation results in an installation needing to use a much different customized workload mix than the two described above. The low I/O density workload mix is defined as a combination of 60% CB-L, 20% WASDB and 20% OLTP-W.

Figure 6 - RMF CPU and Workload Activity Extracts

| MVS PARTI                                                 |                                                       |                                      |                                                                                   |                                           |         | SYSA                                   |                              |                             |                                          |                                       |                                                       |   |

|-----------------------------------------------------------|-------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------|---------|----------------------------------------|------------------------------|-----------------------------|------------------------------------------|---------------------------------------|-------------------------------------------------------|---|

| IMAGE CAP                                                 | ACITY                                                 |                                      |                                                                                   |                                           |         | 37                                     |                              |                             |                                          |                                       |                                                       |   |

|                                                           | PART                                                  |                                      |                                                                                   |                                           |         |                                        |                              |                             |                                          |                                       | OCESSOR DATA -<br>H TIME DATA                         |   |

| NAME                                                      | S                                                     |                                      |                                                                                   |                                           | DEF     |                                        |                              |                             | EFFI                                     |                                       | TOTAL                                                 | _ |

| SYSA                                                      | A                                                     | 80                                   | 0                                                                                 | 30                                        | NO      | 0.0                                    | 2                            | CP                          | 00.2                                     |                                       | 7 00.24.30.58                                         |   |

| SYSB                                                      | A                                                     | 5                                    | 0                                                                                 | 2                                         | YES     | 0.0                                    | 2                            | CP                          | 00.01                                    | 1.16.19                               | 6 00.01.20.20                                         | 2 |

| SYSC                                                      | A                                                     | 15                                   | 0                                                                                 | 5                                         | NO      | 0.0                                    | 2                            | CP                          | 00.03                                    | 3.45.18                               | 2 00.03.52.50                                         | 2 |

| *****                                                     | ****                                                  | ****                                 |                                                                                   |                                           |         | ******<br>A D A                        |                              |                             |                                          | *****                                 | *****                                                 |   |

| ******                                                    |                                                       |                                      | =STANI                                                                            | V O R F                                   | K L O i |                                        |                              |                             |                                          | ****                                  | ******                                                |   |

| snip                                                      | 3Y: P                                                 | OLICY                                | =STANI<br>Stand                                                                   | V O R F<br>DARD<br>dard Po                | K L O A | AD A                                   | СТІ                          | VI                          | ГҮ                                       |                                       | **************************************                |   |

| snip REPORT 1                                             | 3Y: P                                                 | OLICY                                | =STANI<br>Stand                                                                   | V O R F<br>DARD<br>dard Po                | CLOA    | AD A                                   | СТІ                          | V I '                       | ГҮ                                       | SE<br>IOC                             | RVICE<br>579383                                       |   |

| snip  REPORT I  TRANSACT AVG MPL                          | BY: PFIONS                                            | OLICY<br>T<br>9 A<br>8 E             | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUTI                                        | V O R F<br>DARD<br>dard Po<br>-TIME       | CLOA    | A D A M.SS.TTT 1.14.263 1.14.206       | CTI I SSO RES                | V I S                       | I/O<br>881.8<br>1.6                      | SE<br>IOC<br>CPU                      | RVICE<br>579383<br>6411K                              |   |

| snip  REPORT I  TRANSAC' AVG MPL ENDED                    | BY: P<br>FIONS<br>110.3<br>110.3                      | OLICY<br>T<br>9 A<br>8 E<br>6 Q      | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUTI<br>UEUED                               | N O R F<br>DARD<br>dard Po<br>-TIME       | CLOA    | M.SS.TTT<br>1.14.263<br>1.14.206       | CTI I SSC RES                | V I '                       | I/O<br>881.8<br>1.6<br>1.1               | SE<br>IOC<br>CPU<br>MSO               | RVICE<br>579383<br>6411K<br>4658K                     |   |

| snip  REPORT I  TRANSACT AVG MPL ENDED END/S              | BY: PFIONS 110.3 110.3 227 2.5                        | OLICY T 9 A 8 E 6 Q 3 R              | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUTI<br>UEUED<br>/S AFI                     | N O R F  DARD  dard Po  TIME  ION  FINITY | CLOA    | M.SS.TTT<br>1.14.263<br>1.14.206<br>25 | C T I                        | V I ' DASD : CHRT   SP      | I/O<br>881.8<br>1.6<br>1.1<br>0.2        | SE<br>IOC<br>CPU<br>MSO<br>SRB        | RVICE<br>579383<br>6411K<br>4658K<br>376059           |   |

| snip  REPORT !  TRANSAC! AVG MPL ENDED END/S #SWAPS       | BY: P<br>FIONS<br>110.3<br>110.3<br>227<br>2.5<br>217 | OLICY T 9 A 8 E 6 Q 3 R 2 I          | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUT:<br>UEUED<br>/S AFI<br>NELIG:           | DARD dard Po-<br>TIME ION FINITY          | CLOA    | M.SS.TTT<br>1.14.263<br>1.14.206<br>25 | C T I                        | DASD : CHRT : SP NN SC PEND | I/O<br>881.8<br>1.6<br>1.1<br>0.2<br>0.3 | SE<br>IOC<br>CPU<br>MSO<br>SRB<br>TOT | RVICE<br>579383<br>6411K<br>4658K<br>376059<br>12025K |   |

| snip  REPORT 1  TRANSAC' AVG MPL ENDED END/S #SWAPS EXCTD | FIONS<br>110.3<br>110.3<br>227<br>2.5<br>217          | OLICY T 9 A 8 E 6 Q 3 R 2 I 0 C      | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUT:<br>UEUED<br>/S AFI<br>NELIG:<br>ONVERS | DARD dard Po-<br>TIME ION FINITY IBLE     | K L O A | M.SS.TTT<br>1.14.263<br>1.14.206       | C T I I  S SSC  RES  CON DIS | V I ' DASD : CHRT   SP      | I/O<br>881.8<br>1.6<br>1.1<br>0.2<br>0.3 | SE<br>IOC<br>CPU<br>MSO<br>SRB<br>TOT | RVICE<br>579383<br>6411K<br>4658K<br>376059           |   |

| snip  REPORT !  TRANSAC! AVG MPL ENDED END/S #SWAPS       | FIONS<br>110.3<br>110.3<br>227<br>2.5<br>217          | OLICY  T 9 A 8 E 6 Q 3 R 2 I 0 C 8 S | =STANI<br>Stand<br>RANS<br>CTUAL<br>XECUT:<br>UEUED<br>/S AFI<br>NELIG:           | DARD dard Po-<br>TIME ION FINITY IBLE     | K L O A | M.SS.TTT<br>1.14.263<br>1.14.206<br>25 | C T I I  S SSC  RES  CON DIS | DASD : CHRT : SP NN SC PEND | I/O<br>881.8<br>1.6<br>1.1<br>0.2<br>0.3 | SE<br>IOC<br>CPU<br>MSO<br>SRB<br>TOT | RVICE<br>579383<br>6411K<br>4658K<br>376059<br>12025K |   |

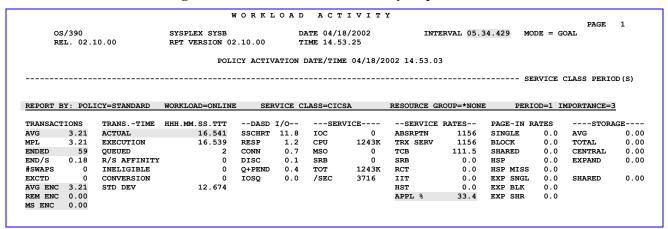

You can compute your own I/O density by looking at the RMF Workload Activity Report for the total interval and the RMF Partition Data Report (both shown in Figure 6). In this example, the DASD SSCH rate for the entire interval (Policy summary report) is 881.8 SSCHs per second. There were 30 MSUs used during the interval, so the I/O density is 881.8 / 30 = 29.4. This is only slightly under the guideline of 30. We're finding many sites with I/O density rates of 12 to 18. Please note that the IBM published MSUs for the z990 and z890 are for software pricing and are 10% less than the approximate capacity of the machine. If this were a z890 or z990, the calculation would be: 881.8 / (30 / .90) = 26.5.)

You can also find a SAS program on our Web site to calculate the I/O density for each of your systems over many intervals at **www.watsonwalker.com/lowio.txt**. The program is designed to handle data stored in an MXG, NeuMICS or ITSV (ITRM) SAS database. An example of output from this program is shown in Figure 7. Please notice how the I/O density can vary a great deal from one LPAR to the next running on the same physical machine. Also, notice that all LPARs would be considered "low I/O," because they are running I/O densities lower than IBM's limit of 30.

The concept of low I/O was introduced by IBM in 1999 when installations were upgrading from a G4 to a G5 or G6 machine. These new machines were significantly faster than the G4 and IBM determined that installations with a low I/O density appeared to perform more like CBW2 (which is very CPU intensive) than any other workload. (The CBW2 workload was renamed to CB-L for the zSeries LSPRs.) This was documented in a paper written by **Kathy Walsh** of WSC in 1999 and last updated March 2002 [REF008]. This paper only referred to non-online work being affected by the low I/O density. A similar paper was written in October 2003 by **Marty Dietch** of IBM, but it only referenced the older machines and not the z990 [REF011].

Figure 7 - I/O Density Report

```

BoxScore V1.6, Watson and Walker, Inc.

17:08 Wednesday, March 24, 2004

I/O Density - DASD I/Os per Second per MSU

Average Minimum Maximum

T/O

T/O

T/O

Density Density

Density

CPU Type

MVS Level

System

z/OS 01.04

z/OS 01.04

SYSA

2064-110

18.5

5.3

1475.3

SYSB

2064-110

18.1

4.0

458.7

2084-310 z/OS 01.04

29.7

SYSC

4.8

3496.2

15.6

SYSD

2084-310 z/OS 01.04

1.3

1294.0

2084-310

z/OS 01.04

1166.1

SYSE

24.1

2.8

```

IBM now feels that the low I/O classification also relates to the z990s. The original LSPR manual [REF004] didn't mention low I/O when the z990s came out. On 15Jan2004, a brief mention of it was added to the LSPR manual [REF004]. Unfortunately, this reference was not added to the Web site, but only as part of Chapter 4 (*Using LSPR Data*) in the manual. An update was made on 2Apr2004 that contains the z890 updates and describes the three new customized workload mixes, including the low I/O content workload mix in Chapter 4.

Based on IBM's performance metrics at the back of the LSPR manual, we calculate the I/O densities for each of the IBM workloads to be:

CB-L = 28 CB-S = 62 WASDB = 9 OLTP-W = 6 OLTP-T = 52

IBM claims that this low I/O density situation occurs because of the move to significantly faster CPs. They say that this was true with the previous G4 to G5/G6 machines, and now occurs when moving from z900s to z990s. Although we are not sure we can justify the use of CB-L based on intuitive logic (and because of the I/O densities mentioned above), we agree with IBM that it much more closely approaches the actual performance that our customers are seeing. The problem for most installations occurs because this is so different from prior years where people successfully used the primitive workloads such as CB84, TSO, CICS/DB2 and IMS for both capacity planning and before/after comparisons.

Because IBM now feels the low I/O condition applies to 80% of the z990 installations, we've also added it as a third customized workload mix to our zSeries CPU Chart and BoxScore.

#### LOIO - Low I/O Workload Mix

The low I/O workload mix is a custom workload mix designed for a system that has a low I/O rate. It is computed in the IBM manner by taking the harmonic mean of 60% of the CB-L workload, plus 20% of the WASDB workload, plus 20% of the OLTP-W workload.

This is a specialized zSeries workload mix that you will not find in IBM's LSPR tables, but it is described in the LSPR manual. It may prove to more accurately match your environment if you run on an image that has a low I/O density.

What does this mean to you? If you're one of the 80% of installations who have a low I/O density, then your expectations should be much closer to the low I/O workload mix than to the MIX workload.

#### And Even Newer Workloads

Just as we were completing this newsletter, we discovered one more reference to customized workload mixes. We don't know yet how these newly defined workload mixes will be used by IBM.

The **zSeries 990 Technical Guide**, **SG24-6947-00**, didn't mention the low I/O concept or customized workload mixes in the original Jul2003 edition. The draft (**SG24-6947-01**) that was published 7Apr2004 contains several new customized workload mixes, including the low I/O content workload mix (section 8.8.1).

Table 1 shows the new workload mixes described in this z990 Technical Guide. We don't know whether these will eventually be documented in the LSPR manual or not.

Workload WASDB **OLTP-W** CB-L CB-S **OLTP-T** MIX 20% 20% 20% 20% 20% TI-MIX 30% 10% 30% 30% TD-MIX 45% 15% 20% 20% TM-MIX 52.5% 17.5% 15% 15% CB-MIX 75% 25% LoIO-MIX 60% 20% 20%

Table 1 - New z990 Customized Workloads

The workloads are described as:

- TI-MIX Transaction intensive

- TD-MIX Transaction dominant

- TM-Mix Transaction moderate

- CB-Mix Commercial batch mix

- LoIO-Mix Low I/O content

One of the changes to note is the difference in the customized commercial batch mixed workload. The zPCR tool was using a combination of 50% CB-L and 50% CB-S. The newer z990 Technical Guide uses a combination of 75% CB-L and only 25% CB-S.

Now that we've described both the primitive and customized workloads, let's look at the LSPRs for each of the newer machines - the z900s, z890s and z990s.

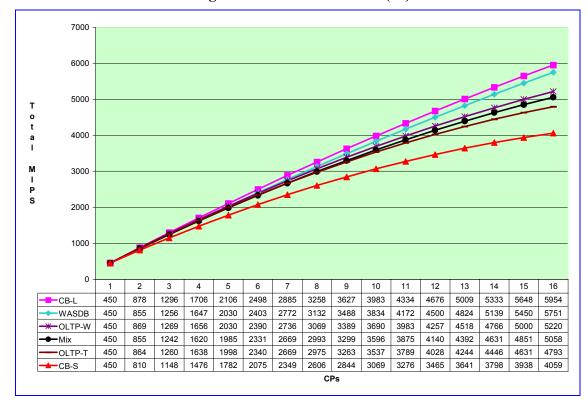

#### z900 LSPRs

The z900 processors became available in May 1999 and the original benchmarks for them were run using OS/390 R10 on a z900 2064-1C1 processor. As mentioned earlier, the MIX workload was a combination of some 31-bit workloads and some 64-bit workloads, and was even more unreliable than in the past in forecasting expected performance. More consistent z900 LSPR ratings came from running the benchmarks created for the z990 processor on the z900s. These are the CB-L, CB-S, WASDB, OLTP-W and OLTP-T workloads that we described earlier.

#### Analyzing the Latest z900 LSPRs

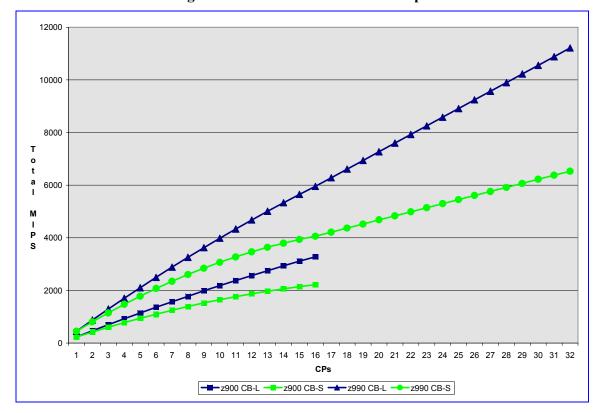

Converting the z900 ITRRs to MIPS, we see the five workloads and the MIX workload as shown in Figure 8. (Editor's Note - We're using MIPS as the basis of our charts, but you would produce exactly the same charts if you used ITRRs. For most of our examples, we use just the CB-L and CB-S workloads because they represent the two extremes of all the workloads and are easier to view. The other workloads always fall between these two workloads, both for the z900s and z990s.) As the number of CPs increases, the variance of the MIPS by workload increases. CB-L appears to do much better at the higher end (more CPs), and CB-S does much worse at the higher end. In fact, we can see that CB-L workloads always do much better than other workloads.

What does this mean to you? If you make the mistake of using the average (MIX) MIPS, either from us or from someone else, you could be very far off in your expected performance. The MIX workload provides lower MIPS than the CB-L, WASDB and OLTP-W workloads, but provides higher

Figure 8 - z900 Total MIPS Using z/OS LSPRs

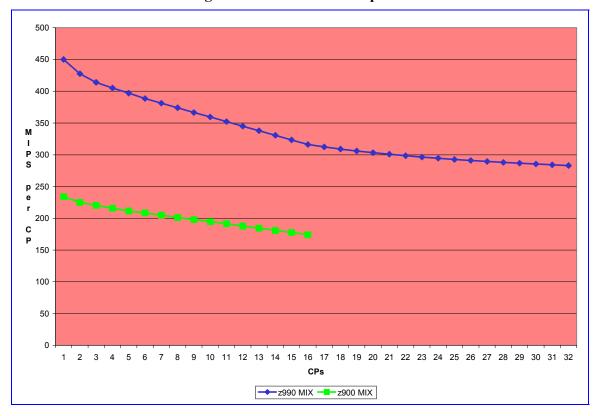

Figure 9 - z900 MIX MIPS per CP

MIPS than the CB-S and OLTP-T workloads. Using MIX, your expectations could be wrong, and in fact, will almost always be wrong. The only way to properly predict the performance is by using the correct set of workload estimates. We'll cover this subject in more detail later.

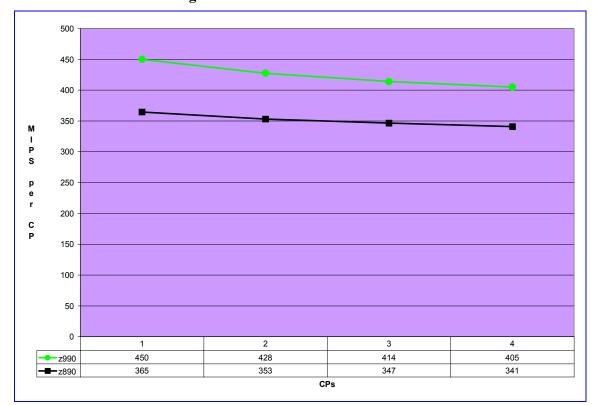

Figure 8 looked at the total MIPS for each workload, but Figure 9 provides a view of the LSPR using MIPS per CP. Although the total MIPS predict the total capacity of a machine, the MIPS per CP predict the speed of each processor. A specific job usually runs on only one processor at a time, and the speed gives an indication of the change in the amount of CPU time used by the job. In Figure 9 we've graphed both the z900 processors and the z990 processors. Notice how the MIPS per CP decreases as more processors are added to the configuration. This drop is the multiprocessing effect (or 'MP' effect) due to the overhead associated with processor communication (such as SIGPs). Traditionally, this drop has been about 4-5% for the first few processors, changing to 2-3% as you add a greater number of processors.

What does this mean to you? Because of this inherent drop in CPU speed when more processors are enabled, it's important to assign the minimum number of CPs to any image. Reducing the number of processors will allow each to run at a higher speed. We'll discuss the z990 processors from this graph a bit later.

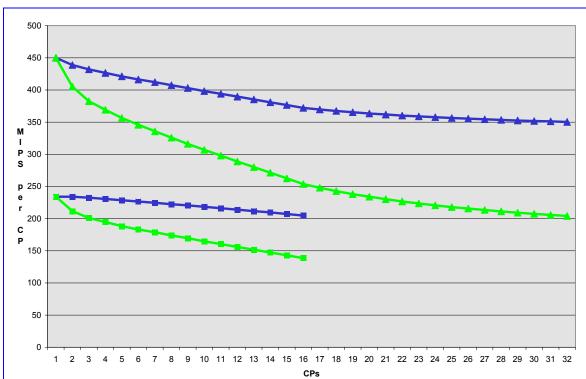

Some workloads do better with more processors, while others don't. This is easily seen in Figure 10. For now, let's concentrate on the two bottom lines on the graph. These represent the MIPS per CP for the z900 CB-S workload (bottom line) and the z900 CB-L workload (the line above it). You see that the MP effect is less noticeable for the CB-L work. In other words, performance doesn't degrade as much for CB-L work when more processors are added.

Figure 10 - CB-L and CB-S MIPS per CP

**--**z900 CB-L **--**z990 CB-L **--**z900 CB-S **-**z990 CB-S

**Figure 12 - z990 Total MIPS (32)**

From what we've seen thus far, the CB-L workloads show improved relative performance over the CB-S workloads on the z900. The CB-L workloads consistently provide more MIPS than CB-S workloads, especially as the number of processors increase.

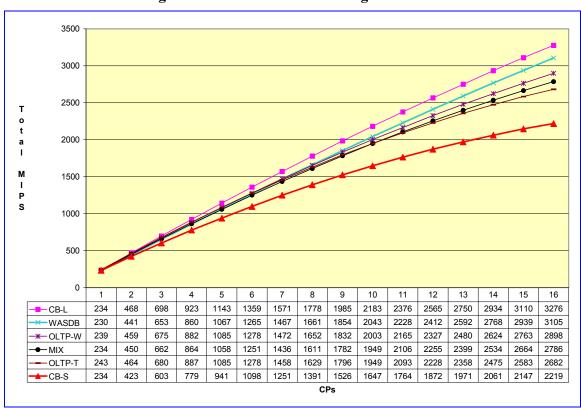

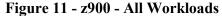

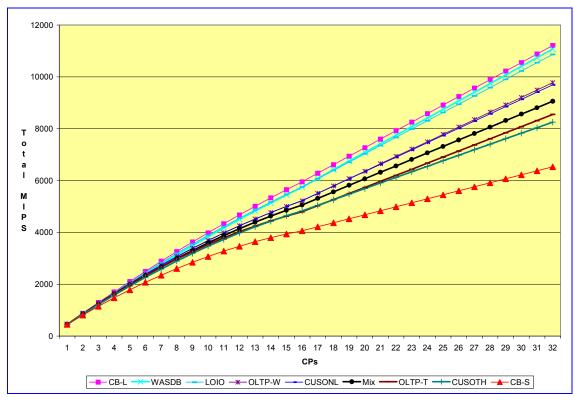

We used the MIX workload for our initial analysis in Figure 2. But now let's take a look at both the primitive workloads and customized workload mixes together. In Figure 11 we can make the following observations for the z900:

- The CB-L, WASDB and LOIO workloads are somewhat similar (top three lines of the plot) and perform the best of all the workloads plotted. CB-L is the best (i.e. produces more MIPS), followed by LOIO and then WASDB.

- 2. The OLTP-W and CUSONL workloads are almost identical (next two lines from the top, but superimposed on one another).

- 3. The MIX workload is the next line down and is almost identical to the OLTP-T workload until they start to separate at about 11 CPs.

- 4. The OLTP-T and CUSOTH workloads are also very similar (second and third line from the bottom).

- 5. The CB-S workload is the worst of all those plotted (bottom line).

- 6. On a 16-way machine, the difference between the highest and lowest total MIPS is over 1000 MIPS (from 3276 MIPS for CB-L to 2219 MIPS for CB-S). This is over a 47% difference quite significant!

**Figure 13 - z990 Total MIPS (16)**

- 7. On a 16-way machine the difference between the highest and lowest MIPS per CP (Figure 10) is 66 MIPS (205 for CB-L versus 139 for CB-S).

- 8. In the previous section, we discussed the difference between the z900 LSPRs derived from OS/390 and z/OS. The most important point there was that the CBW2 work, which had not been part of the MIX for OS/390, is now included in CB-L, which is part of the MIX for the z/OS LSPRs.

### z990 LSPRs

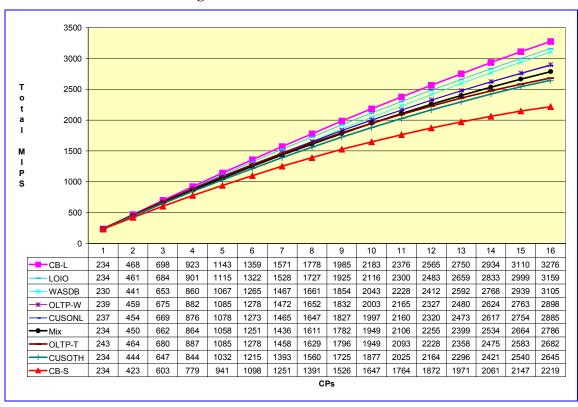

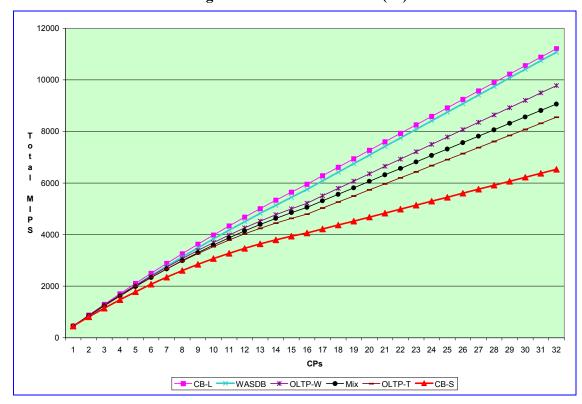

Now let's take a look at the LSPRs for the z990s. Figure 12 shows the MIPS by workload for the z990. Notice how there seems to be a slight wiggle around the 16-CP area? During IBM's initial testing, none of the existing operating systems supported more than 16 logical processors. As noted in the LSPR manual and LSPR Web site, IBM chose to overcome this limitation by using two LPARs for the benchmarks, running each LPAR as a 16-way. We can now understand why this variation occurs by first looking at Figure 13, which shows just the first 16 CPs. Notice that as the number of CPs increases, the range of MIPS between CB-L and CB-S increases even more.

Because the testing environment used the same number of logical CPs as physical CPs, the performance was almost equivalent to running on dedicated CPs. IBM then used a straight extrapolation between the 16-way and 32-way. This extrapolation is fairly easy to see in Figure 12, and appears to be the cause for the wiggle between the 16-way and 17-way that we see in the same figure.

Figure 14 - CB-L and CB-S Total Mips

Understanding that, it doesn't explain what we see in Figure 14. The darker lines are CB-L MIPS and the lighter lines are CB-S MIPS. The top two lines are for the z990 and the bottom two lines are for the z900. We can see from this chart that CB-S work starts to drop off more rapidly than CB-L work from the 8-way to the 16-way, while CB-L work doesn't have nearly as much degradation (if any) as the MP increases. But because of what we assume is the straight line extrapolation, this degradation does not continue past 16 CPs. This makes us quite uncomfortable about the projected performance and capacity estimates for the models above the 16-way models.

Going back to Figure 9 and looking at the MIX MIPS per CP for the z990 (top line), we can see this same phenomenon. The machines above the 16-way don't have the same degradation as the first 16 CPs. This doesn't seem reasonable, and gives us even more reason to doubt the capacity claims of the larger MPs (i.e. the larger n-ways). The same observations can be made regarding Figure 10, where the CB-L MIPS per CP have almost no degradation. We just don't think this seems reasonable. We could be wrong, of course, but we suggest being **VERY** careful when planning for anything larger than a 16-way z990.

We were using the MIX workload for our first analysis in Figure 2. But let's take a look at all of the customized and primitive workloads together, as shown in Figure 15. We can make the following observations for the z990:

1. The CB-L, LOIO and WASDB workloads are similar (top three lines of the plot).

Figure 15 - z990 - All Workloads

- 2. The OLTP-W and CUSONL workloads are also similar (next two lines from the top and overlapped).

- 3. The MIX is the next line down and does not seem to be representative of any of the other workloads, although it certainly represents a midpoint (this is an important concept).

- 4. The OLTP-T and CUSOTH workloads are quite similar (second and third lines from the bottom).

- 5. The CB-S workload is the worst and stands apart from all others (bottom line).

- of the z990 workloads tend to cluster together (i.e. look very similar). This means there is little difference between CB-L, LOIO and WASDB. But it's all relative, and we need to be careful of the scale of the plot. There is still a significant difference of 345 MIPS between CB-L and WASDB for the 32-way. There is also little difference between OLTP-W and CUSONL (87 MIPS for the 32-way). The same is true for OLSTP-T and CUSOTH (although why this is true is probably no more than coincidence).

Figure 16 - z890-x70

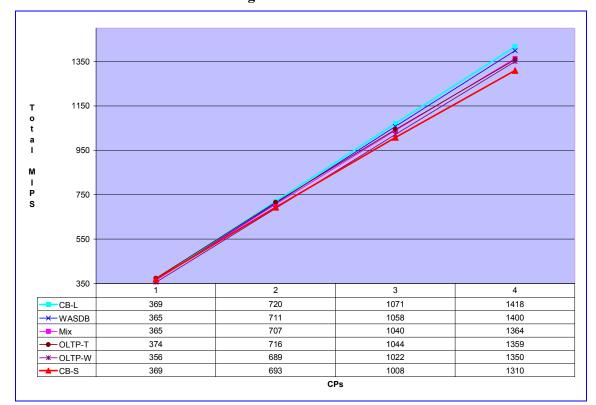

### z890 LSPRs

The z890s, announced in April of 2004, support a maximum of four CPs. Therefore, you won't find the major differences in the various workloads that are seen on the faster processors. At the high end, however, the difference between CB-S and CB-L could still be more than 100 MIPS. Figure 16 shows the largest of the z890s, the x70 models.

There appears to be far less degradation due to MP overhead, however (at least according to the ITRRs). This can be seen more easily in Figure 17 in the MIPS per CP plot. We don't fully understand this behavior because the z890 engines are simply z990 engines modified to run slower.

Because we haven't talked to any z890 customers, we don't know whether the low I/O condition applies to the z890s. There is more about the z890s in our *What's New?* section starting on page 45.

Figure 17 - z890 & z990 MIPS Per CP

## **Bibliography**

This is the bibliography for the *LSPR Update* article that began on page 3. Some of these items may also be referenced in the next article on *z990 Expectations*.

We would like to make an observation about several of the IBM articles and our CPU Chart. Throughout the IBM documentation, there are many references to the invalid use of MIPS from consultants 'or vendors' CPU Charts. They say repeatedly that MIPS are invalid and that the only thing that is reliable is the LSPR ITRRs. We don't believe that their warnings apply to our CPU Charts. Their main concern is that most CPU Charts, with ours being the only exception we know about, only publish a single MIPS value for a machine. This is usually based on the MIX ITRR. As we've mentioned in this article, we don't agree with that method either, and it's the reason our CPU Charts contain MIPS for all of the workloads. We even include the customized workloads for which not even IBM publishes ITRRs.

The second problem with most other MIPS charts is that they have only a single chart. But as both we and IBM recommend, the relative capacity of a machine can only be determined by looking at ratings that come from the same LSPR set of benchmarks. We do that by having a separate z/OS CPU Chart and by identifying the LSPR benchmark set in a column within the OS/390 CPU Chart. Because we base our MIPS on the LSPR ITRRs, we feel very confident that we reflect the most accurate view of the processor capacities, while still using the MIPS that are more familiar for most installations.

- REF001 IBM LSPR Web site www.ibm.com/servers/eserver/zseries/lspr

- REF002 Cheryl Watson's zSeries CPU Chart, April 2004; Cheryl Watson's OS/390 CPU Chart, April 2004

- REF003 Cheryl Watson's TUNING Letters: 2003 No. 3, pages 23-25; 2001 No. 2, pages 35-36; 2000 No. 5, pages 49-50; 1997 No. 4, pages 10-26

- REF004 **IBM Large Systems Performance Reference, SC28-1187-09**, 13May2003; update on 15Jan2004; update on 2Apr2004

- REF005 SHARE Long Beach session 2513, JoAnne Brown, Processor Sizing, www.share.org

- REF006 SHARE Long Beach session 2514, Walt Caprice, WSC Short Stories and Tall Tales z990 Performance Considerations, www.share.org

- REF007 WSC Presentation PRS135, **Kathy Walsh**, *Information on Capacity Planning for S/390 G5 and G6 Processors using LSPR data*, 28Mar2002, **www.ibm.com/support/techdocs**

- REF008 **IBM eServer zSeries 990 Technical Guide SG24-6947-01** draft, 7Apr2004 (but no mention of low I/O in SG24-6947-00, Jul2003), **www.redbooks.ibm.com**

- REF009 CMG 2000 Proceedings, **Dr. Sudhir R. Nath** of Wells Fargo Services Company, *Harmonic Mean Analyses Of CPU Speeds*, **www.cmg.org** (Members Only section of the Web site)

- REF010 Gregory V. Caliri of BMC Software, Large Scale Processor Reference (LSPR) And Its Implications, www.bmc.com/offers/performance/whitepapers/docs/2003/

Large Scale Processor Implications.pdf

- REF011 Oct/Nov2003 z/Journal, **Marty Deitch**, *IBM's LSPR Benchmark Results: The Truth About Mainframe MIPS*, **www.zjournal.com/PDF/deitchoct.pdf**

- REF012 BoxScore, www.watsonwalker.com/boxscore.html

- REF013 Cheryl Watson's TUNING Letters: 1998 No. 6, page 28; 1998 No. 4, page 37

- REF014 Cheryl Watson's TUNING Letter 2002 No. 4, page 20

- REF015 Cheryl Watson's TUNING Letters: 1998 No. 6; 2002 No. 3, pages 28-33; 2003 No. 5, pages 37-41; other references:

February 1991, FOCUS: PR/SM

March 1991, Reducing I/O Elongation

May 1991, Amdahl's MDF

December 1991, Dedicated and Shared LPARs

July 1992, Defining a Sysprog LPAR

Sept/Oct 1992, PR/SM Overhead

May/June 1993, PR/SM Changes (SP 4.3)

July/Aug 1993, FOCUS: LPAR Update (EMIF, MDF, SP 4.3)

1997, No. 4, LSPRs and You

1998, No. 1 & 2, Configuration Changes

REF016 - WSC White Paper WP100258 - Performance Considerations When Moving to Fewer Faster CPUs, www.ibm.com/support/techdocs

## Focus: z990 Expectations

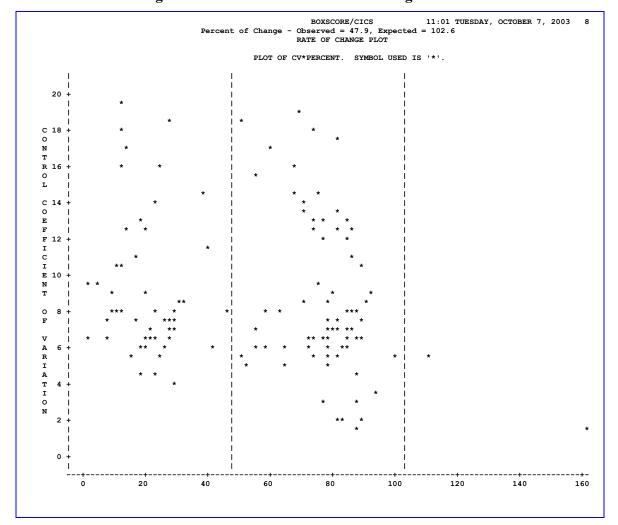

The z990 (T-REX) processor has been in the field since September 2003 and we've been getting quite a bit of feedback on its performance. The results are varied, but overall we feel that customers are not seeing the performance they expected. In this article, we'll first cover the results from our z990 customers (using both our BoxScore product and other tools). Then we'll explain the causes for these missed expectations, both real and perceived. And finally, we'll present our recommendations. When we mention LSPRs, it will be helpful if you've already read our *LSPR Update* beginning on page 3. That article is an important prerequisite to understanding what is happening on the z990s.

- BoxScore Results

- Reasons for Underperformance

- z900 to z990 Migration

- More BoxScore Results

- Our Conclusions and Recommendations

### **BoxScore Results**

In early November of 2003, we started getting feedback from our BoxScore customers who had installed z990s. As you probably know, our software product, BoxScore, is designed to determine whether you are getting the capacity you expect after a hardware or software upgrade. [Please see REF012 for additional information on BoxScore.]

So far, we've only seen moves from z900s to z990s. With one exception, all BoxScore sites are seeing between 8% and 12% fewer MIPS than expected for batch processing using the traditional primitive workloads. Four CICS installations were experiencing between 10% and 15% fewer MIPS than expected. That one exception experienced performance that was 4% better than expected for their batch work on their new z990. Their CICS work, however, failed to meet expectations by about 10%.

At least two of the installations went back to IBM with the BoxScore results and were able to get hundreds of thousands of dollars back in credits. (Note: the customers told us these were credits due to the underperformance of the z990. IBM says that credits haven't been given due to underperformance but because of improper sizing. All of the installations reporting underperformance asked that their names not be used.)

Our long-time readers will remember that we've previously seen underperformance in BoxScore results during moves to new processors. You might recall the problem with CMOS machines and COBOL programs that used subscripting instead of indexing. [REF013] Or you might remember the problems with the change to high-speed cache processing on the z900s that caused increases in run times for SAS and other products. [REF014] In both previous cases, customers were able to identify from the BoxScore reports the specific programs that were not meeting expectations and determine the commonalities. But thus far, we have not identified any specific application or program type that seems to be causing the variance from the expected z990 results.

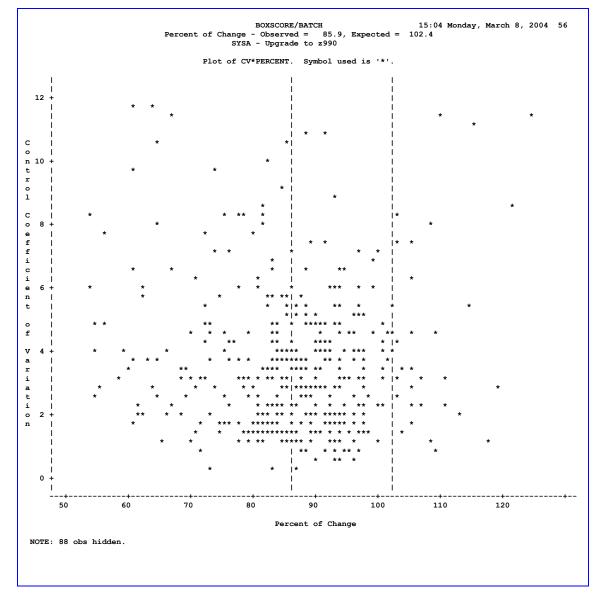

Figure 18 - BoxScore Percent of Change Plot

Refer to Figure 18, which shows a BoxScore Percent of Change Plot. This is an example of a move from a z900 2064-113 to a z990 2084-310, which should have provided double the MIPS per CPU. The plot for this change shows an increase of 85.9% in effective MIPS per CPU (as seen by the middle vertical line of '|'), but the expected change was 102.4% (the rightmost vertical line of '|') so the customer was very disappointed. The points on the far left are those jobs performing the worst, while the points on the right are those doing the best. As you can see, however, the work is quite clustered and evenly distributed around this 85.9% increase. This BoxScore run was made using the CB-S LSPRs, because the installation had successfully used CB-S LSPRs in the past for moving batch between two machines.

Another BoxScore report is shown in Figure 19. This reports that from an LPAR point of view, the batch work experienced an 11.1% reduction from the expected result, in both capacity and speed. Looking at it from the CEC point of view, the batch work experienced an 8.1% reduction from the expected result.

**Figure 19 - BoxScore Summary Report**

| V1R6 (c) Watson & Walker,                               | Inc.                                 |                                               | SCORE/BATCH<br>- CPU per I/O                          | 15:04 Monday         | , March 8, 2004 49                    |

|---------------------------------------------------------|--------------------------------------|-----------------------------------------------|-------------------------------------------------------|----------------------|---------------------------------------|

|                                                         | + The work a<br>+ 46.2%<br>+ between | nalyzed during<br>decrease in the two environ | g this period e<br>CPU time per I/<br>onments analyze |                      |                                       |

| +-BoxScore/BATCH: -11.1%                                |                                      |                                               |                                                       |                      |                                       |

| +                                                       |                                      |                                               |                                                       | + + Expected         |                                       |

| + From an LPAR view,                                    | •                                    | +                                             |                                                       | -+ +                 | +                                     |

| + STUDY                                                 | +                                    | +                                             | + +                                                   |                      | + + +                                 |

| + had 11.1% less                                        |                                      |                                               |                                                       | + + Max 412.1        |                                       |

| + speed and capacity                                    | + 3 2340 0                           | + 2007 1                                      | + +                                                   | + +<br>+ + Avg 335.6 | + + + + + + + + + + + + + + + + + + + |

| <pre>+ than expected from + published performance</pre> |                                      | + 2087.1                                      | + + -11.18                                            | + + AVG 335.6<br>+ + | + 298.2 +                             |

| <pre>+ published performance + estimates.</pre>         |                                      |                                               |                                                       | + +<br>+ + Min 335.6 |                                       |

| +                                                       | +                                    | + 1/24.3                                      | + + -20.00                                            | + + MIN 333.0        | + 240.3 +                             |

| +                                                       | ·<br>-+                              | <b>+</b>                                      |                                                       |                      |                                       |

| +-BoxScore/BATCH: -8.1%<br>+                            | + Expected                           | + Observed                                    | + +                                                   | + + Expected         | + Observed +                          |

| + From a CEC view,                                      | +                                    | +                                             |                                                       | -+ +                 | ++                                    |

| + STUDY                                                 | +                                    | +                                             | + +                                                   | + +                  | + +                                   |

|                                                         |                                      |                                               |                                                       | + + Max 398.3        |                                       |

| + speed and capacity                                    | +                                    |                                               | + +                                                   | + +                  | + +                                   |

| + than expected from                                    |                                      |                                               |                                                       | + + Avg 306.9        |                                       |

| + published performance                                 |                                      | +                                             | + +                                                   | + +                  | + +                                   |

| + estimates.                                            | + Min 3069.0                         | + 2328.9                                      |                                                       | + + Min 306.9        |                                       |

| <b>±</b>                                                | +                                    | +                                             | + +                                                   | + +                  | + +                                   |

Figure 20 shows an LPAR view of the migration. (By the way, we use "control" to identify the old machine or situation and "study" for the new.) We've underlined some of the items that we want to mention. The first underlined item shows that this move was from a z900 2064-113 processor to a z990 2084-310 processor. The next two underlined items show that the LPAR had 11 and 7 logical CPs assigned out of the 13 and 10 physical CPs on those boxes. The ratio of logical to physical CPs went from 1.6 to 1.9, which is a little greater, but not enough to cause significant LPAR overhead. The next three underlined items show that we expected an ITRR of 1.56, but saw an ITRR of 1.43, representing an underperformance of 8.1%. Please note that all of these results were calculated based on the CB-S workload. These results are typical of most of our customers; the results for CICS were usually much worse.

Starting in November, because all of our BoxScore customers were seeing these types of results, we started investigating the reasons for the apparent underperformance. The articles in this newsletter are the result of the last six months of investigation, analysis of z990 migrations, conversations with our customers and discussions with IBM. We think we understand what is happening, and we will try to explain it to you in the remainder of this article.

Figure 20 - BoxScore Identification and CPU Comparison Reports

| 2004 51                       |            | BOXSCORE  | /BATCH - | Dropping | Outliers |      | 15:04 M     | onday, Jan 8,   |

|-------------------------------|------------|-----------|----------|----------|----------|------|-------------|-----------------|

| /1R6 (c) Watson & Walker, Inc |            |           | CDII Co  | mparison |          |      |             |                 |

| TRO (C) Watson & Walker, Inc  | •          |           | CFO CO   | mparison |          |      |             |                 |

| Item                          | Control    | Study     |          | Delta    | % Delta  | ITRR | Comments    |                 |

|                               |            |           |          |          |          |      |             |                 |

| ystem Identification:         |            |           |          |          |          |      |             |                 |

| System                        | SYSA       | SYSA      |          |          |          |      |             |                 |

| Model-Version                 | 2064-113   | 2084-310  |          | ****     |          |      |             |                 |

| Common name for processor     |            | 2084-310  |          | ****     |          |      |             |                 |

| Manufacturer                  | IBM        | IBM       |          |          |          |      |             |                 |

| MVS release                   | z/OS 01.04 | z/OS 01.0 | 4        |          |          |      |             |                 |

| Architecture mode             | 64-bit     | 64-bit    |          |          |          |      |             |                 |

| Central storage               | 12288MB    |           | 12288MB  | 0MB      | 0.0%     |      |             |                 |

| Number of logical CPUs        | 11.0       |           | 7.0      | -4.0     |          |      | WWCB061-T   | # of log. CPU   |

| Number of physical CPUs       | 13.0       |           | 10.0     |          | -23.1%   |      |             | # of phys. CP   |

| LPAR status                   | SHR        |           | SHR      | 5.0      | 20.11    |      |             | LPAR used in    |

| LPAR weight (avg)             | 660.0      |           | 410.0    | -250.0   | -37.9%   |      |             | IRD decreased   |

| Number of active LPARs        | 6.0        |           | 6.6      | 0.6      | 10.0%    |      |             | # LPARs inccr   |

| Total number of LPs in CEC    | 21.0       |           | 19.3     | -1.7     |          |      |             | " 221210 211002 |

| LPAR LPs to CP ratio          | 1.6        |           | 1.9      | 0.3      |          |      | WWCB127-W   | LP to CP rati   |

| Weight of other LPARs (avg)   |            |           | 586.0    |          |          |      | MIODEL / II | 22 00 01 1401   |

| Percent of CEC this LPAR      | 66.0       |           |          |          | -37.6%   |      | WWCB131-W   | % of CEC decr   |

| Total CPU busy                | 801.9      |           |          |          | -33.5%   |      |             | CPU busy is 1   |

| Avg CPU busy                  | 72.9       |           | 76.2%    |          | 4.5%     |      |             |                 |

| Max CPU busy                  | 96.2       | -         | 98.4%    |          |          |      |             |                 |

| Min CPU busy                  | 13.0       |           | 13.7%    |          |          |      |             |                 |

|                               |            | -         |          |          |          |      |             |                 |

| peed of one CPU (physical):   |            |           |          |          |          |      |             |                 |

| Expected SU/second            | 8724.10    | 17003     | .18      | 8279.08  | 94.9%    | 1.95 | 5           |                 |

| Expected avg MIPS/CPU         | 151.6      |           | 6.9      | 155.3    |          |      |             | Expected fast   |

| Expected max MIPS/CPU         | 211.5      |           | 8.3      | 186.8    |          |      |             | Weight increa   |

| Expected min MIPS/CPU         | 151.6      |           | 6.9      | 155.3    |          |      |             | # LPARs incre   |

| Observed MIPS/CPU             | 151.6      |           | 1.9      | 130.3    |          |      |             | CPU is faster   |

| Change from predicted avg     |            |           |          | -25.0    | -8.1%    |      |             |                 |

| Machine capacity (physical):  |            |           |          |          |          |      |             |                 |

| Expected avg MIPS             | 1971.0     | 306       | 9.0      | 1098.0   | 55.7%    | 1.56 | WWCB032-I   | Expect more c   |

| Expected max MIPS             | 2749.5     |           | 2.5      | 1233.0   |          |      |             | LP to CP ratio  |

| Expected min MIPS             | 1971.0     | 306       | 9.0      | 1098.0   | 55.7%    | 1.56 | WWCB129-W   | % of CEC incr   |

| Observed MIPS                 | 1971.0     |           | 8.9      | 848.0    |          |      |             | More capacity   |

| Change from predicted avg     |            |           |          | -250.1   | -8.1%    |      |             |                 |

|                               |            |           |          |          |          |      |             |                 |

### Reasons for Underperformance

While investigating the situations seen by our BoxScore installations, we believe we've discovered three main causes for the underperformance. Although we think the third reason is the most significant, we'll cover the other two first and then turn our attention to the third reason. (We also believe there is still another reason for underperformance for CICS, but we haven't been able to track it down. We'll cover that in a later issue as we acquire more information.)

#### LPAR Configuration

Because the z990 is twice as fast as the z900, most installations are making a move to faster but fewer processors. If the installation does not change the number of LPARs, having fewer CPs can lead to an unacceptable ratio of logical CPs to physical CPs. When there are too many logical CPs to physical CPs (more than 3 to 1), the amount of LPAR overhead can be quite high. One site, for example, went from a 12-way z900 to an 8-way z990 with 30 logical CPs. Although this was barely acceptable on a z900 (with a ratio of 2.5 to 1), it was simply too much contention on the z990 (with a ratio of 3.7 to 1) and caused additional overhead. In our example in Figure 20, the change was from 1.6:1 to 1.9:1, so the increase in LPAR overhead was minimal.

It should be possible to reduce the number of logical CPs to an acceptable number once you're aware of the problem. This step of planning LPARs should be done before you make a final decision on a processor.

#### Moving to Faster CPs

Because of the significant difference in the speed of the CPs between the two machines (the z990 is rated at 450 MIPS per CP versus the z900 at 234 MIPS per CP), you will probably run into the fewer but faster phenomenon that we described in our TUNING Letter 1996, No. 6. The original issue is on our Web site under "Sample Issues," but we've updated the article for the current machines and included it in this issue starting on page 40.